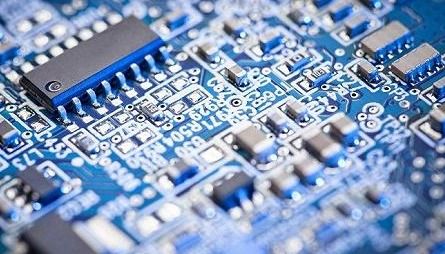

CPLD芯片ICD2053B的原理构造及其在数据采集系统中的应用

引言

在当今数字化、智能化的工业控制和信息处理领域,数据采集系统扮演着至关重要的角色,它作为连接物理世界与数字世界的桥梁,负责实时、准确地获取各类传感器和外部设备的信息。而复杂可编程逻辑器件(CPLD)以其高度的灵活性、强大的逻辑处理能力和可靠的时序性能,成为实现高效、稳定数据采集逻辑控制的核心器件之一。ICD2053B作为一款典型的CPLD芯片,其独特的原理构造使其在数据采集应用中展现出显著优势。

一、CPLD芯片ICD2053B的基本原理与内部构造

CPLD(Complex Programmable Logic Device)是一种基于乘积项(Product-Term)结构、集成度较高的可编程逻辑器件。ICD2053B作为其中一员,其内部构造核心在于实现灵活的数字逻辑功能。

- 基本架构:

- 宏单元(Macrocell):这是CPLD的基本逻辑单元。ICD2053B内部包含数百个宏单元,每个宏单元通常由一个可编程的与阵列(实现组合逻辑)、一个触发器(实现时序逻辑)以及选择器(用于配置输出路径和反馈路径)构成。宏单元是实现具体逻辑功能(如计数器、状态机、译码器)的基础。

- 可编程互连阵列(PIA):这是CPLD架构的关键。它是一个全局性的、可编程的布线资源池,将所有宏单元的输入和输出连接起来。通过PIA,任何一个宏单元的输出可以灵活地路由到几乎任何一个宏单元的输入,从而实现了高度复杂逻辑电路的内部连接,确保了信号的灵活布通和时序的一致性。

- 输入/输出单元(I/O Block):负责芯片与外部电路的接口。每个I/O引脚都可以被独立配置为输入、输出或双向端口,并可以设置输出驱动能力、上拉/下拉电阻、电压标准(如3.3V LVTTL)等,使其能够直接连接各种传感器、ADC(模数转换器)、存储器或微处理器。

- JTAG编程接口:用于芯片的逻辑功能配置(编程)和在系统测试,支持ISP(在系统编程)功能,便于系统升级和维护。

- 工作原理:用户使用硬件描述语言(如VHDL或Verilog)描述所需的数字逻辑功能,通过开发软件进行综合、布局布线,生成一个包含逻辑与互连信息的编程文件(如JEDEC文件)。将该文件通过JTAG接口下载到ICD2053B中,即可配置其内部的与阵列、宏单元功能及PIA的连接关系,使其“变身”为特定的数字电路系统。一旦编程,配置信息通常存储在非易失性存储器(如EEPROM或Flash)中,上电即运行,无需外部配置芯片。

二、ICD2053B在数据采集系统中的应用优势

在数据采集系统中,ICD2053B主要扮演“智能接口”和“逻辑控制中枢”的角色,其应用优势体现在:

- 高度集成的接口逻辑控制:数据采集系统通常需要连接多种传感器(模拟/数字)、ADC芯片、存储器(FIFO、RAM)以及上位机(如通过UART、SPI、并行总线)。ICD2053B可以集成所有这些接口的控制逻辑,例如:

- ADC控制:产生精确的ADC启动转换信号、读取转换完成标志、并按照特定时序读取转换结果数据。

- 通信协议实现:高效实现SPI、I2C、UART、自定义并行总线等通信协议,完成与传感器或主处理器的数据交换。

- 多路复用与通道管理:控制多路模拟开关,实现多路传感器信号的巡回采集。

- 精确的时序生成与管理:数据采集对时序要求极为严格。CPLD基于硬件并行处理,能够生成纳秒级精度的时钟、使能、片选等控制信号,确保ADC采样、数据锁存、传输等各环节严格同步,避免软件控制可能带来的时序抖动和不确定性。

- 数据预处理与缓冲:在将数据发送给主处理器(如MCU、DSP)之前,ICD2053B可以进行初步的数据处理,如:

- 数字滤波:实现简单的均值滤波、去抖动等算法。

- 格式转换:将ADC的原始数据转换为工程单位值,或进行字节序重组。

- 数据打包与缓存:将多通道数据打包成特定帧格式,并存入片内逻辑实现的FIFO缓冲区,以匹配主处理器较慢的读取速度,实现数据流的平滑。

- 可靠性高,响应迅速:作为硬件逻辑执行,不受软件跑飞、中断延迟等问题影响,系统抗干扰能力强,对关键事件的响应是确定且即时(微秒甚至纳秒级)的。

- 设计灵活,易于修改:当采集需求变化(如增加通道、改变通信协议、调整采样率)时,只需修改HDL代码并重新编程CPLD,无需改变PCB硬件,极大缩短了开发周期和降低了升级成本。

三、典型应用实例分析

假设一个工业现场多通道温度、压力数据采集系统:

- 系统构成:多路热电偶/RTD(通过信号调理电路)、多路压力传感器、高精度多通道ADC芯片、微处理器(MCU)、ICD2053B CPLD、通信模块。

- ICD2053B的核心功能实现:

- 逻辑控制核心:CPLD内部构建一个主状态机,协调整个采集流程。

- 通道扫描控制:按预设顺序,循环输出通道选择信号至模拟多路开关。

- ADC驱动:为选中的通道产生精确的ADC启动转换脉冲,监测转换结束信号,并在恰当时钟沿读取ADC输出数据。

- 数据预处理:对读取的原始数据进行查表线性化补偿(针对热电偶)、或简单的标度变换。

- 数据缓冲与接口:将处理后的通道数据与通道号打包,写入一个异步FIFO。实现一个SPI或并行总线接口逻辑,响应MCU的读取请求,将FIFO中的数据高效、无误地传输给MCU进行进一步处理或上传。

- 看门狗与异常处理:可集成硬件看门狗逻辑,监控采集流程,在超时或异常时产生复位或中断信号。

通过上述设计,MCU得以从繁琐、高实时的底层时序控制中解放出来,专注于更高层的任务调度、算法处理和人机交互,整个系统的可靠性、实时性和效率都得到显著提升。

结论

CPLD芯片ICD2053B凭借其基于乘积项和全局互连阵列的确定性硬件结构,提供了高度灵活、可靠且高速的数字逻辑实现平台。在数据采集系统中,它将分散的接口控制、精确的时序管理、初步的数据处理等功能集成于单一芯片,不仅简化了系统硬件设计,更大幅提升了数据采集的实时性、同步性和整体可靠性。随着数据采集系统向更高速度、更多通道、更复杂预处理的方向发展,像ICD2053B这样的CPLD将继续发挥其不可替代的核心作用。

如若转载,请注明出处:http://www.chuanqingkeji.com/product/58.html

更新时间:2026-04-14 08:27:16